Table of Contents

Flipflops

Ein Flipflop (dt.: bistabiler Multivibrator oder bistabile Kippstufe) ist eine Schaltung, die zwei verschiedene Zustände annehmen und damit 1 Bit Information speichern kann. Wir haben eine eifnache Flipflop-Schaltung auf Grundlage von Transistoren schon in einem früheren Kapitel kennengelernt. In diesem Kapitel lernen wir eine Schaltung auf Grundlage von Logikgattern kennen und erweitern sie zum taktgesteuerten Master-Slave JK-Flipflop. In den nachfolgenden Kapiteln bauen wir aus Flipflops dann Zähler und Schieberegister.

RS-Flipflop

Ein RS-Flipflop (“Rücksetz-Setz-Flipflop”, engl.: SR-Flipflop (“Set-Reset-Flipflop”)) besitzt zwei Eingänge S (“Set”) und R (“Reset”). Liegt S auf high und R auf low, so wechselt der Ausgang Q zu high und verbleibt so lange in diesem Zustand, bis S auf low und R auf high gesetzt werden. In diesem Zustand verbleibt das Flipflop dann wieder beliebig lange, bis S wieder auf high und R auf low gesetzt werden.

Der Ausgang $\overline{\mathrm{Q}}$ (sprich “Q quer” oder “nicht Q”) zeigt immer das Gegenteil von Q an.

Aufbau aus NOR-Gattern

Baue die Schaltung auf, probiere sie aus und schau' Dir zum Verständnis der Funktionsweise unbedingt das folgende Video von Ben Eater an:

Baue die Schaltung auf, probiere sie aus und schau' Dir zum Verständnis der Funktionsweise unbedingt das folgende Video von Ben Eater an:

D-Flipflop

Bevor Du die drei nächsten Schaltungen baust, schau' Dir das entsprechende Video von Ben Eater an:

Da R und S zum Umschalten des Flipflops immer gegengleich stehen müssen (high und low oder low und high), könnte man doch gleich den Wert von S abgreifen, negieren und an R anlegen…

Heraus kommt das D-Flipflop:

Zum Negieren “missbrauchen” wir ein zusätzliches NOR-Gatter. Da das IC 74HCT02 vier davon besitzt, können wir die Schaltung so mit nur einem IC aufbauen!

Jetzt kann man sich aber fragen, welchen Sinn das ganze hat: Der Zustand des Ausgangs entspricht einfach immer dem Zustand des Tasters! Wo wird denn da noch was gespeichert?

D-Flipflop mit Enable-Eingang

Wir bauen an das D-Flipflop einen Enable-Eingang, so dass der Zustand des Eingangs D nur dann ausgewertet wird, wenn Enable auf high liegt:

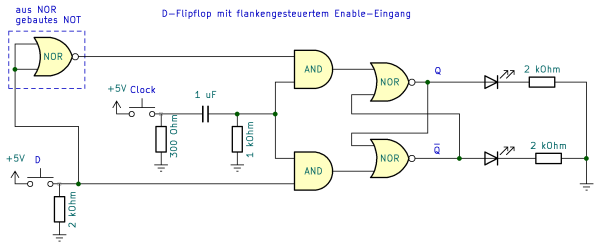

D-Flipflop mit flankengesteuertem Enable-Eingang

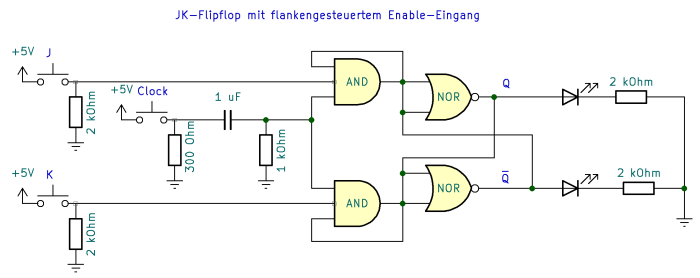

JK-Flipflop

Für viele Anwendungen ist es erwünscht, dass in dem Fall, dass beide Eingänge des Flipflops high sind, mit steigender Taktflanke der Ausgang seinen Zustand wechselt. Diesen Wunsch erfüllt das JK-Flipflop. Schau Dir wieder das Video von Ben Eater an, bevor Du die Schaltung baust:

Das JK-Flipflop hat folgende Zustandstabelle:

| J | K | Clock | $\mathrm Q$ | $\overline{\mathrm{Q}}$ |

|---|---|---|---|---|

| 0 | 0 | rising edge | last state | last state |

| 0 | 1 | rising edge | 0 | 1 |

| 1 | 0 | rising edge | 1 | 0 |

| 1 | 1 | rising edge | toggle | |

| x | x | no rising edge | last state | |

Das Schaltzeichen des JK-Flipflops siehst Du rechts. Meist besitzt es noch einen Reset-Eingang, durch den man es in den Grundzustand ($\mathrm Q == high$, $\overline{\mathrm{Q}} == low$ versetzen kann. Der Balken über dem R bedeutet, dass der Eingang negiert ist, d.h.: Liegt low am Eingang an, so wird das Flipflop in den Grundzustand versetzt, liegt high an, so arbeitet es wie oben beschrieben. Wir müssen also dafür sorgen, dass der entsprechende Pin des ICs an 5 V angeschlossen wird.

Das Schaltzeichen des JK-Flipflops siehst Du rechts. Meist besitzt es noch einen Reset-Eingang, durch den man es in den Grundzustand ($\mathrm Q == high$, $\overline{\mathrm{Q}} == low$ versetzen kann. Der Balken über dem R bedeutet, dass der Eingang negiert ist, d.h.: Liegt low am Eingang an, so wird das Flipflop in den Grundzustand versetzt, liegt high an, so arbeitet es wie oben beschrieben. Wir müssen also dafür sorgen, dass der entsprechende Pin des ICs an 5 V angeschlossen wird.

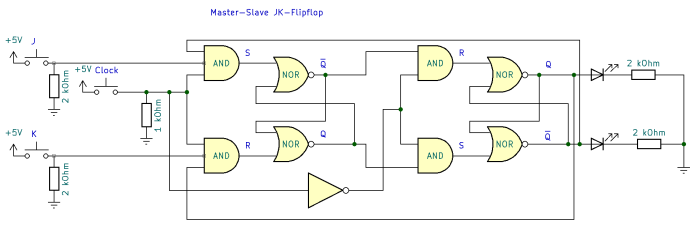

Master-Slave JK-Flipflop

Die obenstehende Schaltung des JK-Flipflops krankt an einer Race-Condition, siehe das folgende Video von Ben Eater:

In der Praxis baut man es daher in einer Master-Slave-Konfiguration:

Wir haben für diesen Zweck das IC 74 HCT 73 vorrätig. Schlag sein Pinout im Datenblatt nach, entwirf eine Testschaltung und baue sie auf!